삼성전자가 D램 미세공정 기술의 `마의 벽`을 넘었다. 10나노대 D램을 세계 최초로 양산했다. 국내외 경쟁사는 아직 20나노 초반대 D램도 주력 공정으로 올리지 못했다. 삼성전자가 10나노대 D램을 양산하면서 후발업체인 미국 마이크론과의 기술 격차를 2년 이상 벌렸다는 것이 전문가 분석이다. PC 수요 역성장, 스마트폰 성장세 둔화로 D램 가격은 하락세에서 좀처럼 벗어나지 못하고 있지만 삼성전자는 공정 전환에 따른 원가 절감으로 경쟁사보다 월등히 높은 이익률을 기록할 전망이다.

27일 업계에 따르면 삼성전자는 최근 회로 선폭이 18나노인 D램 양산을 시작했다. 초기 생산 품목은 PC에 탑재되는 범용 D램이다. 주요 고객사의 특성 테스트를 통과, 일부 물량은 이미 공급까지 마쳤다.

삼성전자는 18나노 D램 비중을 점차 확대하면서 부가가치가 높은 서버, 모바일 D램 생산도 시작한다. 18나노 공정 비중을 확대하기 위해 국내외 협력업체에 조만간 생산 장비를 발주할 예정이다. 일부 협력사는 이미 구두로 발주를 받고 장비 생산에 들어갔다. 올 여름께 발주가 되면 늦은 하반기에 공급, 설치될 전망이다. 18나노 D램의 생산량 증대(램프업) 작업은 여름 이후 시작된다는 의미다.

20나노보다 미세한 10나노대 D램 양산은 업계 전문가들 사이에선 `마의 벽`으로 불린다. D램은 메모리 셀에 배치된 커패시터(축전기)에 전하를 저장하고 이를 통해 0과 1을 판단한다. 공정 미세화가 이뤄지면 셀 면적이 좁아져서 커패시터 용량을 사수하는 것이 점점 어렵다. 바닥 면적이 좁아지면 원통형 커패시터의 수직 길이를 늘려야 한다. 이 경우 공정 과정에서 커패시터가 무너지는 문제가 발생한다. 커패시터 용량 사수 외에도 좁아진 커패시터의 간격으로 인한 노이즈 증가, 전하 유출(터널링), 노광 패터닝 어려움도 풀어야 할 과제였다.

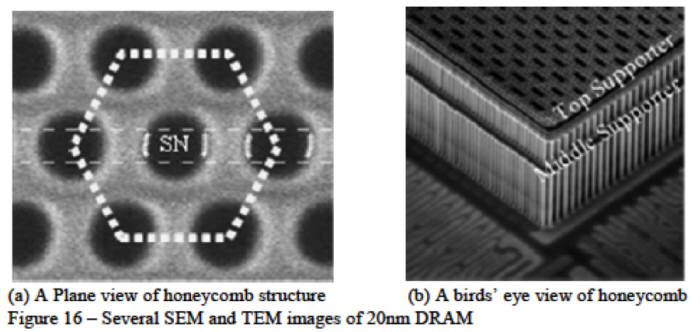

<삼성전자 20나노 D램 셀 구조. 벌집 구조를 채택해 셀 캐패시턴스를 57%나 확대했다.>

<삼성전자 20나노 D램 셀 구조. 벌집 구조를 채택해 셀 캐패시턴스를 57%나 확대했다.>

삼성전자 메모리사업부는 20나노 D램 양산에 활용한 여러 기술을 업그레이드, 18나노 D램에 적용한 것으로 전해졌다. 셀 구조 혁신으로 커패시터 용량을 사수하는 한편 초미세 유전막 형성 기술을 적용, 터널링 현상을 해결했다. 패터닝은 3~4번에 걸쳐 회로 패턴을 새기는 쿼드러플 패터닝 기법을 도입했다. 삼성전자는 초기 18나노 D램 양산품이 경쟁사로 건너가지 않도록 보안에도 각별한 신경을 기울이는 것으로 알려졌다. 업계 관계자는 “양산품을 전달받은 고객사에 특별히 관련 요청을 한 것으로 안다”고 전했다.

삼성전자가 18나노 D램을 양산함에 따라 경쟁사와의 원가 경쟁력 격차가 크게 벌어질 전망이다. D램 가격이 계속 떨어지는 최악의 상황이 발생했을 때 경쟁사는 적자를 봐도 삼성전자는 이익을 낼 수 있다.

SK하이닉스는 20나노 초반대 공정 비중을 늘리고 있다. 1x 나노 D램은 개발을 진행하고 있다. 마이크론은 20나노 초반대 공정 D램을 양산조차 못한 것으로 전해진다.

김경민 대신증권 연구원은 “실적을 보면 국내 업체와 마이크론 간 공정 기술 격차가 상당히 크다는 것을 알 수 있다”고 말했다. 삼성전자와 마이크론 간 D램 공정 기술 격차는 이미 2년 이상 벌어졌다는 것이 전문가들의 설명이다. 당장 마이크론은 적자를 걱정해야 하는 처지에 놓였다.

'관심사' 카테고리의 다른 글

| SK텔레콤 "죽은 父 요금 내라"..현대판 '백골징포' 논란 (0) | 2016.04.01 |

|---|---|

| 삼성전자 1분기 '깜짝실적' 전망…영업이익 6조원 달할 듯 (0) | 2016.03.29 |

| 라인, 일본서 알뜰폰 사업 시작한다 (0) | 2016.03.25 |

| 안투투 "아이폰SE, 2GB 램 탑재.. 13만점대 성능 (0) | 2016.03.22 |

| 애플, iOS 9.3 정식 업데이트 배포 (0) | 2016.03.22 |